[ad_1]

Final time, we seemed over diffpairs, their fundamentals, routing guidelines and the infamous tolerances of PCIe relating to diffpairs. Now, let’s check out the precise alerts that make PCIe tick, in addition to provide you with an outline of which sockets you will get PCIe on.

I separate PCIe sockets into two classes – desktop sockets, that are the same old 1x, 16x, or maybe x4 PCIe sockets we see on desktop motherboards — and cell sockets: mPCIe and M.2. There are additionally sockets like ExpressCard which are nonetheless discovered on some older laptops, however they’ve undoubtedly fallen out of relevance. On cell, M.2 is the best way ahead relating to PCIe – should you’re , I’ve written a brief collection speaking about all the pieces M.2 earlier than.

On these sockets, most alerts will probably be optionally available and a few alerts will probably be socket-specific, however there are some alerts required in any PCIe machine. In fact, the primary group of required alerts is the PCIe diffpairs themselves.

PCIe Is Simply Spicy UART

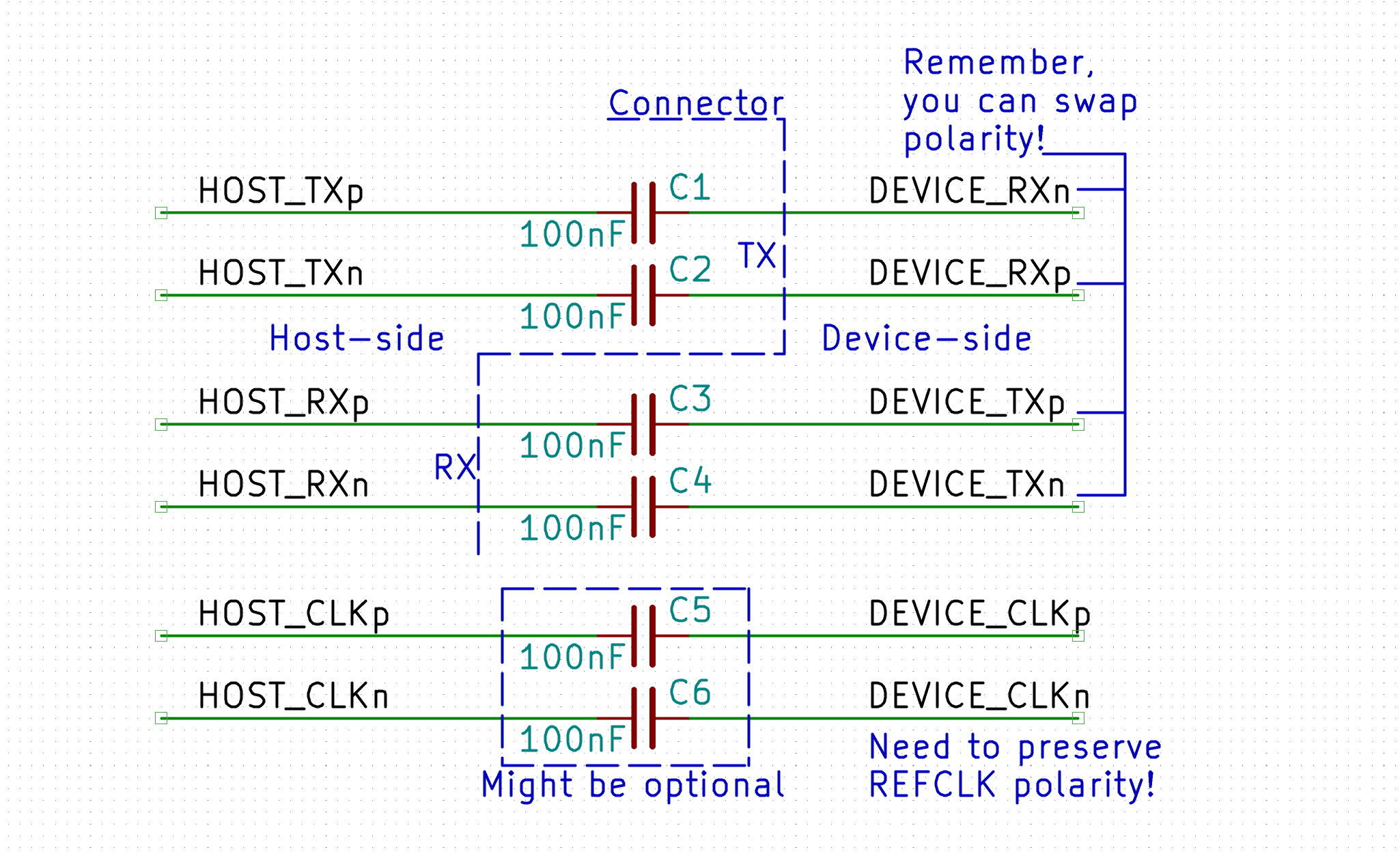

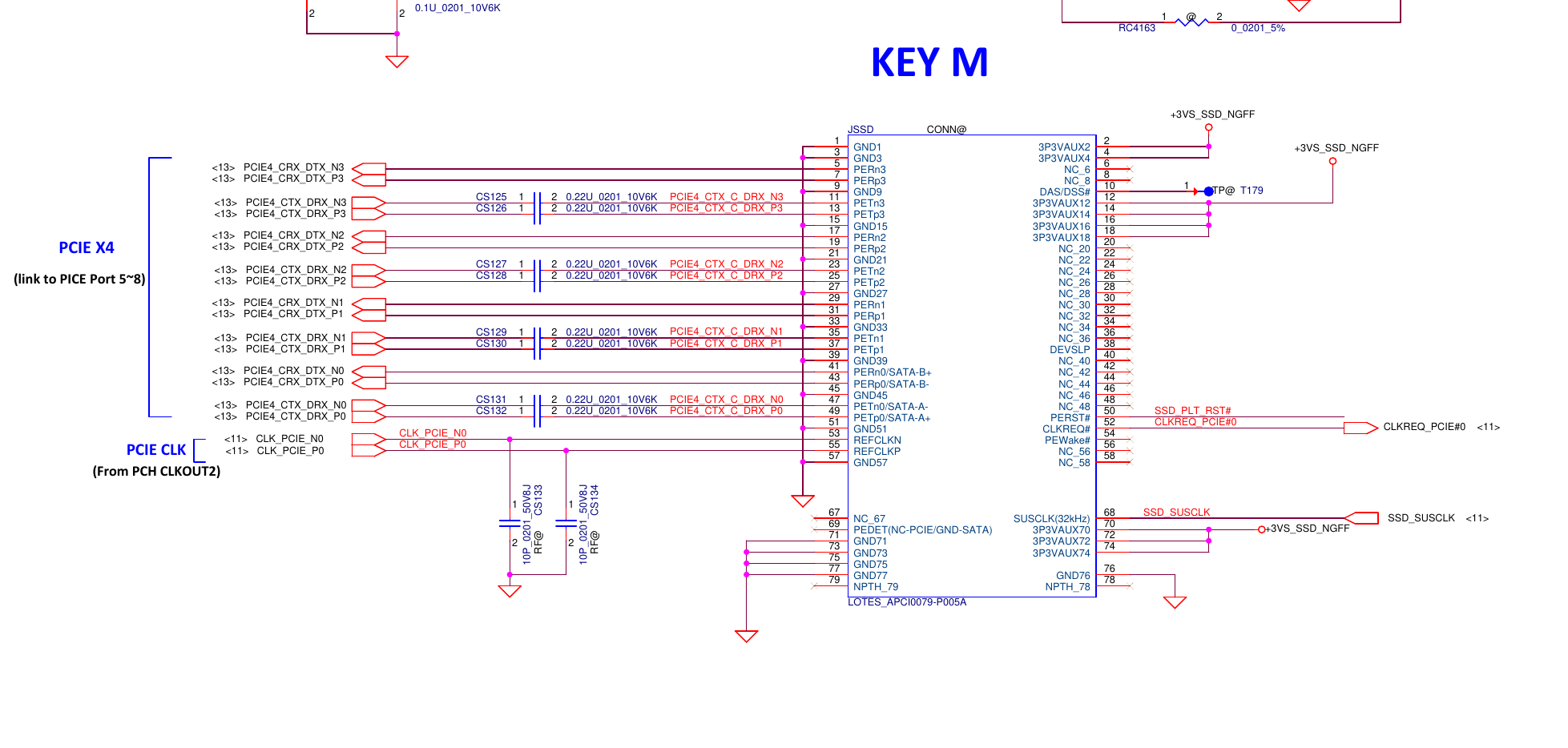

Any PCIe interface has two sorts of diffpairs – TX and RX; for an x1 hyperlink, you should have one TX diffpair and one RX diffpair, and a x16 hyperlink wants sixteen of every. As you would possibly anticipate, RX on one finish connects to TX on one other finish, and vice-versa – it’s similar to UART, however spicy. In fact, should you’re doing a PCIe extender or socket-to-socket adapter of some form, you don’t must do any swapping. In case you’re designing a board for one of many PCIe-carrying extension requirements, the same old naming is host-side. For instance, say you’re placing a PCIe Ethernet controller IC onto a PCB that plugs right into a desktop PCIe socket – join TX and RX of the PCIe socket board to to your Ethernet chip’s RX and TX respectively.

If there’s sturdy indication that this conference has been violated, don’t fret – be sure to match to an current host or machine, and see if you’ll be able to decide whether or not the naming is as-expected or certainly, unexpectedly, flipped. Once more, it’s similar to UART! That stated, there’s additionally AC coupling capacitors positioned in collection on each the TX and RX strains. Particularly in case of PCIe extension playing cards, be it M.2 or desktop PCIe, the conference is putting them on device-TX (host-RX) strains on the machine board, and on the host-TX facet (device-RX) on the host board. This alone is a pleasing divergence from UART relating to design and reverse-engineering.

The third form of diffpair, one which’s invariably current, is REFCLK – a 100 MHz clock diffpair. It’s a speedy clock, and I’m undecided about its full goal, however apparently, it performs an element in decoding the info on TX and RX, particularly, clock restoration – staying important regardless of being orders of magnitudes slower than the GBit-range bandwidth of PCIe TX and RX pairs. In contrast to with RX and TX, you can’t swap the REFCLK polarity willy-nilly. Alternatively, it gained’t harm as a lot you probably have REFCLK cross via a set of vias or two in case it’s worthwhile to flip it – it’s simply 100 MHz. Keep in mind to respect your diffpairs, and also you’ll be good.

REFCLK is required – besides, theoretically, there’s circumstances the place you possibly can omit it, requiring each ends of the PCIe hyperlink to assist recovering this clock from knowledge handed via RX and TX pairs, or generate their very own REFCLK. It sounds fairly life like, but, REFCLK-less PCIe implementations aren’t actually on the market. Even SD-Categorical, a current normal that brings PCIe to SD playing cards for blazing quick entry speeds, didn’t go this route – the one consumer-available REFCLK-less implementation out within the wild is SATA-Categorical, a regular that turned obsoleted by M.2 nearly as quickly as motherboards with SATA-Categorical ports hit the shop cabinets. Because it stands, in order for you your PCIe hyperlink to work, you completely want REFCLK.

And now bit extra concerning the capacitors. You want them on each TX and RX for the hyperlink to work, with ranges from 75 nF to 265 nF relying on PCIe hyperlink technology: 200 nF is an effective all-around worth and 100 nF will work in a pinch. Aside from that, go for 0402 or 0201 package deal, and that’s mainly it. REFCLK doesn’t sometimes want the capacitors, however they shouldn’t harm both, and sure gadgets would possibly require them. Additionally, right here’s one thing puzzling – there’s been at the least one documented case of an inexpensive mass-manufactured WD SSD seemingly omitting its TX-side capacitors, failing to initialize with a customized PCIe host board up till further capacitors have been added on the mainboard facet. It’s not one thing it’s best to do by default – merely a peculiarity that one producer had the gall to create.

The Few Alerts Vital

Then, there’s a trio of single-ended management alerts – CLKREQ, PEWAKE, and PERST. CLKREQ is used for energy saving – the machine normally units CLKREQ low to start out receiving REFCLK, and is ready to de-assert CLKREQ (set it excessive) to sign the host that the host can cease offering REFCLK, saving energy. The CLKREQ sign is peculiar – it’s current on cell gadgets, however isn’t used on desktops, to the purpose the place desktop PCIe slots didn’t even initially have a devoted pin for it. In consequence, the USB3-cable-perusing miner “GPU riser” boards don’t cross CLKREQ via – solely PEWAKE and PERST. In case your host has a CLKREQ pin however the machine doesn’t, floor it; in case your machine has a CLKREQ pin however the host doesn’t, ignore it, in any other case, join them collectively.

Effectively, if the corner-cutting miners hassle to cross PEWAKE and PERST alerts via, then they should be essential, proper? Let’s see. PERST is the reset pin for the PCIe hyperlink, and the host holds it low till all of the clocks (together with REFCLK) and energy rails are secure and different necessities are met for the host to start out speaking PCIe; it’s additionally used for some low-power mode administration. PEWAKE is used for energy administration similar to CLKREQ, and does appear to be required as effectively – that is additionally a device-side-controlled sign. These two alerts are a bit mysterious to me relating to methods you possibly can omit them, so I like to recommend having each of them related except they’re outright unavailable on one of many ends.

Desktop slots even have PRSNT alerts – relying on the hyperlink width, it’s important to brief PRSNT#1 to one of many PRSNT#2 alerts. Not that that is required – PCIe is greater than able to detecting hyperlink width accurately; nevertheless, desktop motherboards do usually want this in apply. It appears to be used for hotplug – one thing that PCIe is technically able to, and which is able to even work should you use a system like Linux; Home windows would possibly simply refuse to course of PCIe hotplug except you dance round your PC chanting magic phrases.

There’s I2C alerts on each desktop PCIe slots and cell slots like mPCIe or M.2. Nonetheless, these alerts are hardly ever ever related on the mainboard – when they’re, it appears to be both the mainboard producer’s whim, or provisions for options like VPro. On server boards, they’re related, inflicting enjoyable issues like some server-originated SAS controllers not working on sure desktop boards with I2C wired as much as the desktop-size slots. If you’re wiring up a host-side PCIe slot, you don’t actually need to wire I2C up, and should you’re wiring up a tool, don’t anticipate I2C to reliably be there. Similar goes for JTAG alerts – they’re utilized in debugging or server environments, and are finest left unconnected except you’re sure your implementation advantages from them within the place the place you’ll use it.

Cell PCIe gadgets normally function on 3.3 V energy, whereas desktop gadgets can run from both 3.3 V or 12 V, for much less or extra highly effective gadgets respectively. In consequence, should you’re including a desktop-sized PCIe socket and also you don’t have 12 V useful, some desktop playing cards would possibly randomly not work. x1 slots are anticipated to offer much less energy on 12 V than bigger slots, and desktop motherboard producers usually benefit from this leeway – should you’re designing an x1 card, don’t anticipate it to offer the complete 75 W (66 W at 12 V), and should you’re designing a motherboard with an x1 slot, the excellent news is that you just don’t want to offer the complete 75 W.

All The Totally different Hyperlink Widths

Each the host facet and the machine facet can have completely different hyperlink widths – the alternatives are x1, x2, x4, x8 and x16, the place the quantity signifies the quantity of pairs getting used; as a result of manner {that a} PCIe hyperlinks operate on the low degree, these should be powers of two. As such, don’t anticipate a x3 hyperlink to work should you in some way join three lanes from a number to a tool – it would downgrade to x2. PCIe is versatile with regard to hyperlink widths – the host and the machine choose the very best frequent denominator. Regardless of in case your host has a x4 hyperlink and your machine is x16, or your host is x16 and your machine is x4, they are going to choose a x4 hyperlink width, utilizing 4 pairs, not bothered that one of many ends has twelve extra to spare. There are very uncommon exceptions to this – particularly, some server-purpose playing cards; that stated, even these are circumstances of “x8 card gained’t operate with a x4 connection” and a 1x hyperlink will nonetheless work as a fallback.

This provides fairly a little bit of flexibility – if both facet doesn’t have sufficient lanes to match the opposite, you possibly can all the time anticipate at the least an x1 hyperlink to work nonetheless. As an example, you possibly can put a x16 GPU right into a desktop x1 slot by slicing a notch within the slot, and maybe shorting the PRSNT pins on the slot – although, guarantee that your card doesn’t need extra slot-provided energy than your 1x slot is prepared to offer, which could very effectively be the case should you’re plugging an additional GPU right into a cut-up 1x slot immediately! In relation to desktop PCIe slots and playing cards, you will note x1, x4, and x16 bodily slot widths, and x8 slots and playing cards being principally a server incidence. There are some low-end GPUs which are truly x8 playing cards, however they use x16 bodily slot card edge width, and identical goes for x2 playing cards – they use x4 slot card edge width. You’ll hardly ever, if ever, see bodily x2 and x8 playing cards or slots.

When doing a multi-lane hyperlink, you need to just be sure you’re connecting lane 0 with 0, 1 with 1 and so forth. There’s apparently a capability to reverse your complete hyperlink in case that may enable you to along with your format – say, in case of an x4 hyperlink, you can join lane 0 to three, 1 to 2, and so forth. Nonetheless, it’s not clear how extensively that’s supported – it appears to be optionally available and never automagic.

And It Will Work No Matter What

Identical to Ethernet, PCIe hyperlink speeds have been rising with every technology, via gradual knowledge fee will increase, encoding kind and different incremental enhancements. Similar story as with the hyperlink widths – there’s nice forwards and backwards compatibility, a Gen1 machine will work in a Gen5 slot, and a Gen5 machine will work in a Gen1 slot, once more, choosing the very best frequent denominator. In fact, the hyperlink would possibly find yourself being throttled from the expectation – should you plug a Gen3 x1 USB3 controller card into the Gen1 PCIe x1 slot on an outdated motherboard, anticipate the USB3 port throughput to be restricted (and naturally, identical goes for connecting GPUs via a x1 hyperlink). Nonetheless, this does imply that sometimes, you don’t want to fret about PCIe generations except you’re aiming for a sure velocity goal.

Fortunately, you probably have any PCIe questions that go critically in-depth, there’s plenty of data on-line, and specs for even the last-gen PCIe 5.0 are fairly straightforward to search out. It may be a bit dense in comparison with what you’re studying proper now, however whenever you go in deep, it would assist. Subsequent time, let’s full your psychological map of PCIe, in order that everytime you got down to stretch the boundaries of PCIe, you understand how to method it!

[ad_2]